一、先进封装简介

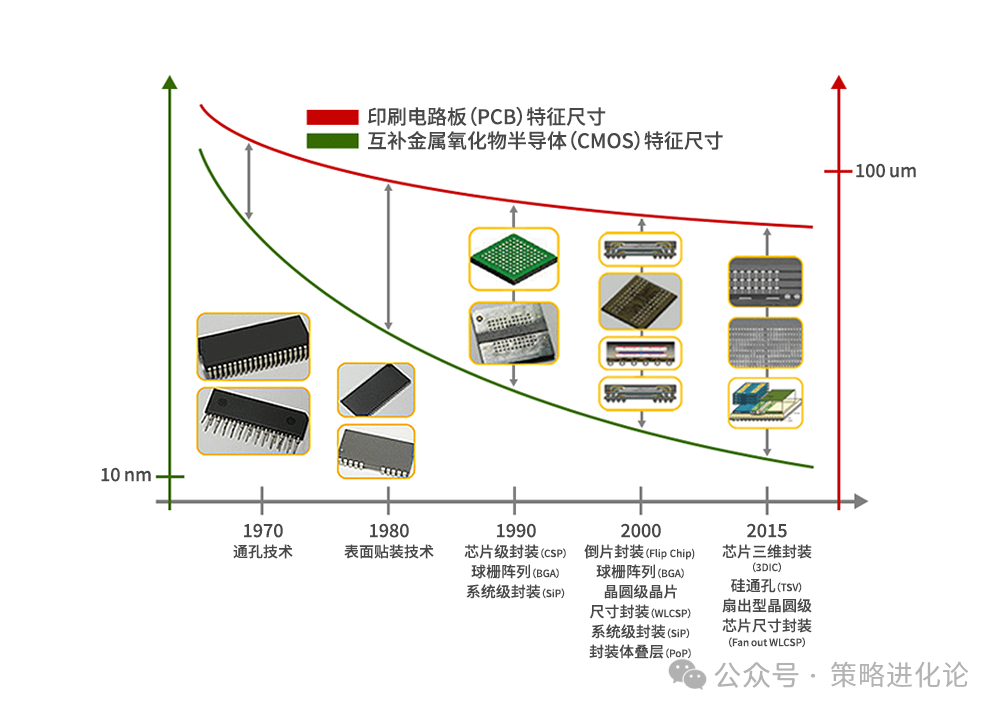

1、封装的技术路径,大致分为四个阶段:

高算力对芯片的传输速率和信息密度有非常高的要求,为了不让封装拖了芯片的后腿,工程师在如何提高连接密度、提高传输速率上想方设法,并且在保证连接质量的情况下,尽可能地降低生产成本、降低功耗、满足小型化等等需要。

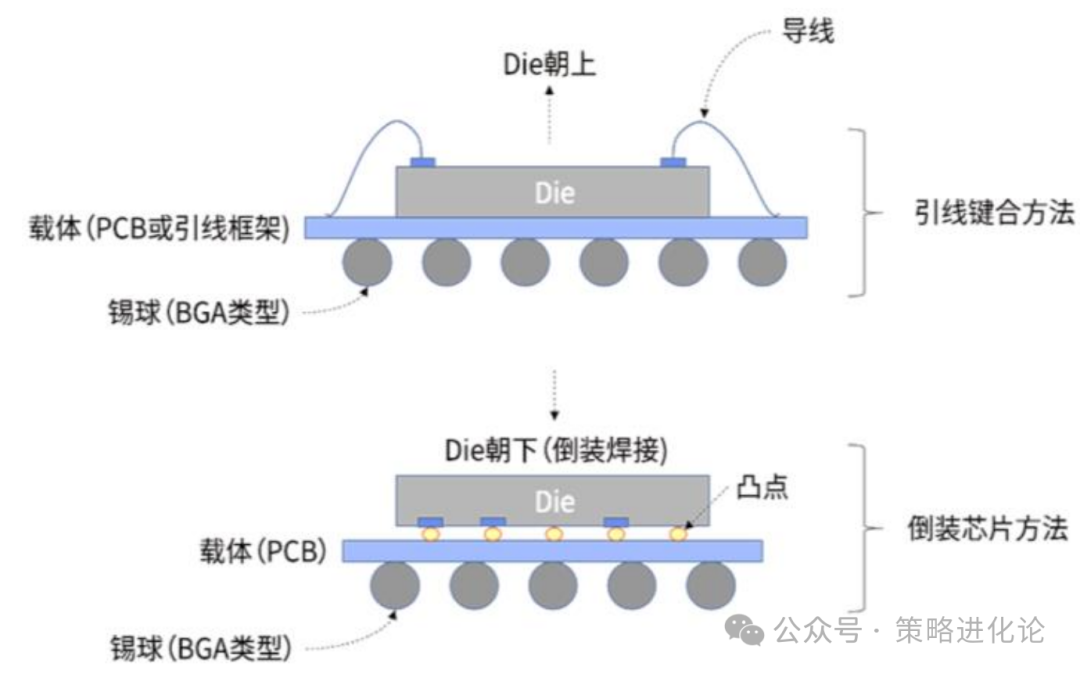

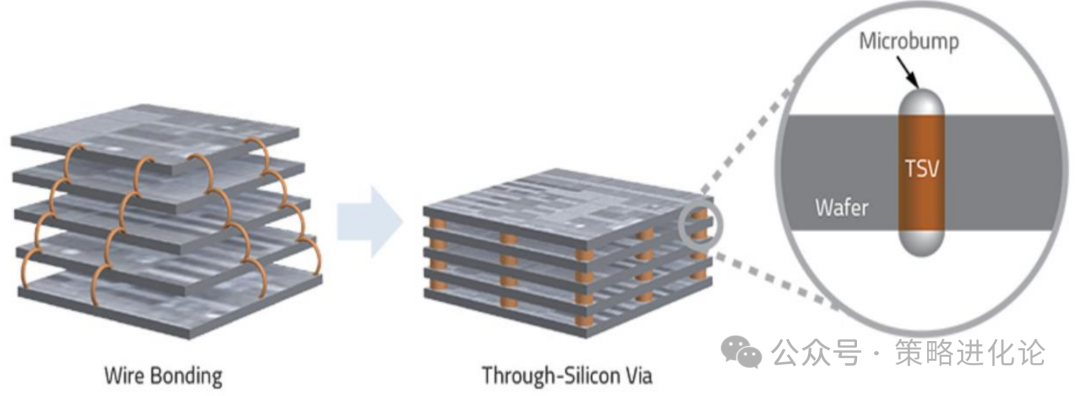

每一代技术之间的本质区别,就是芯片和电路的连接方式的区别。键合法发展史:引线键合(Wire Bonding)→倒装芯片键合(Flip Chip Bonding)→硅穿孔(TSV)

2、先进封装的几个关键技术

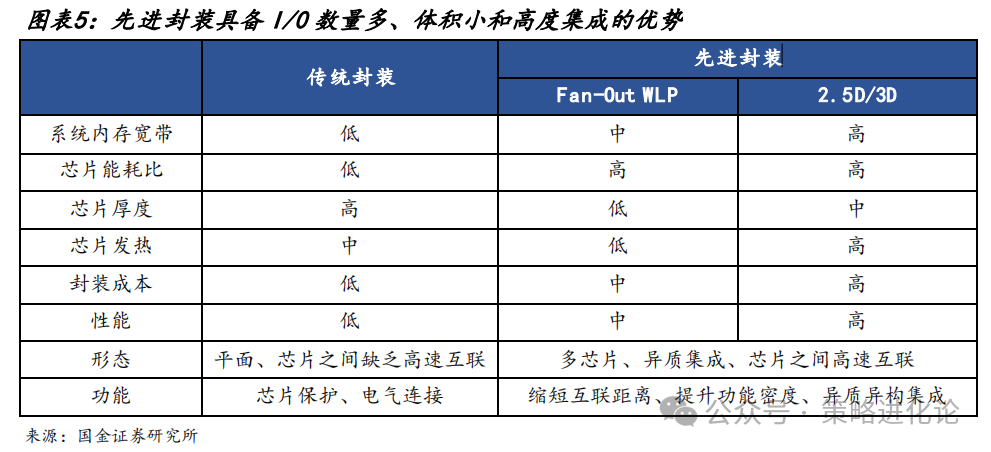

3、先进封装的优势

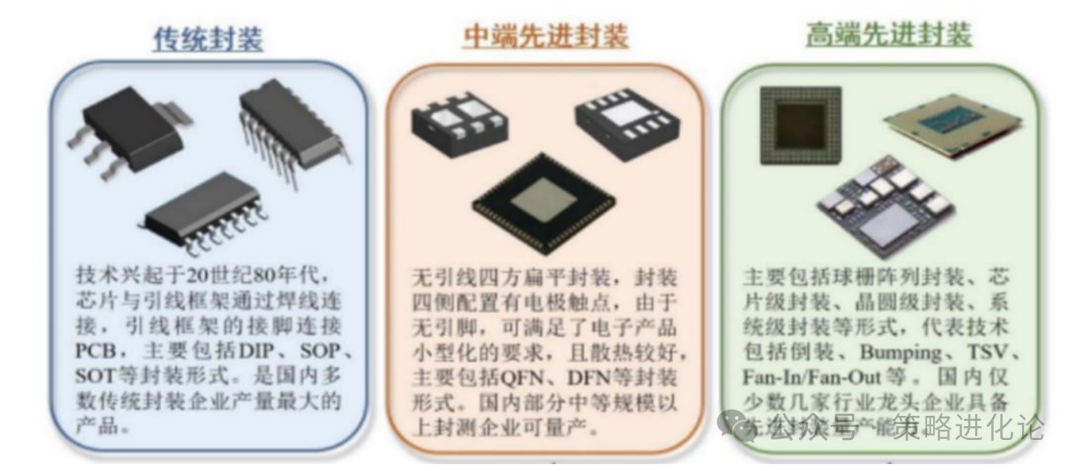

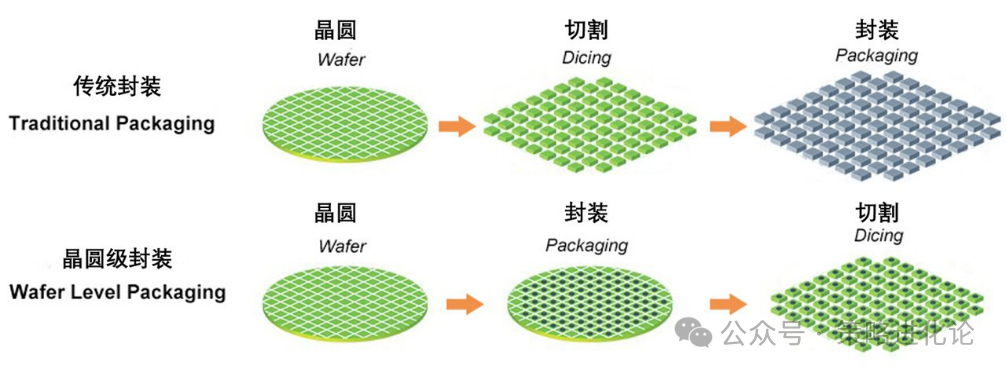

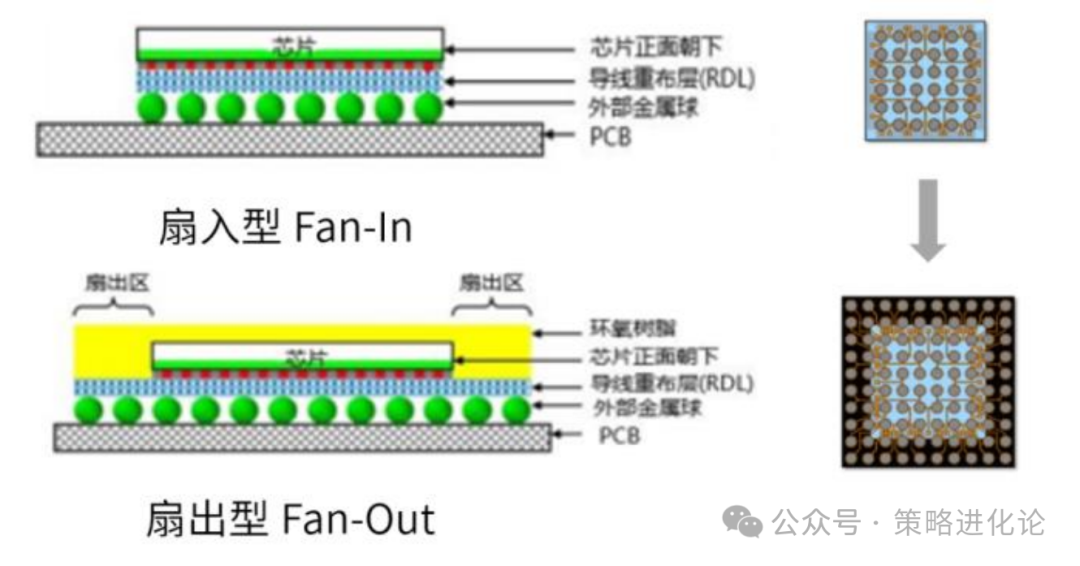

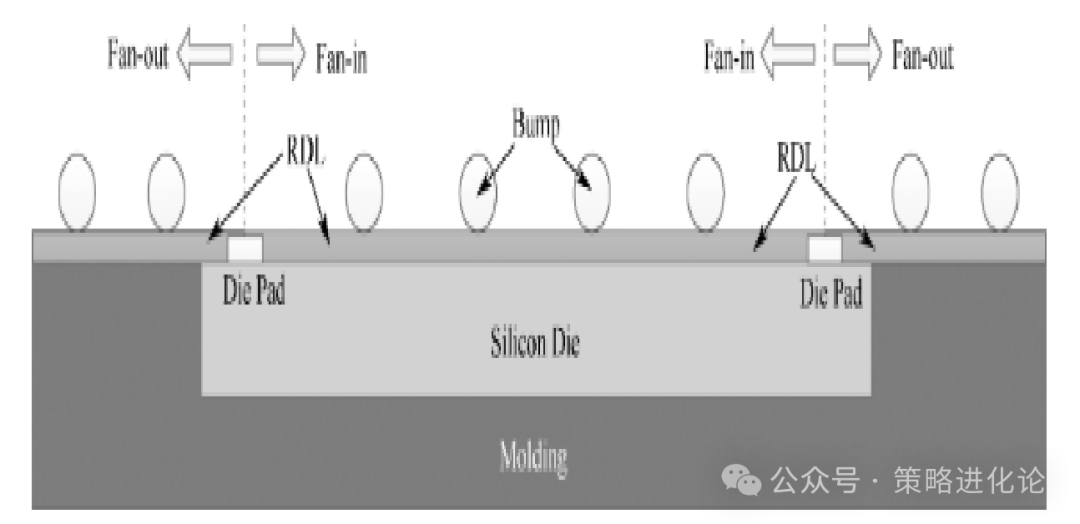

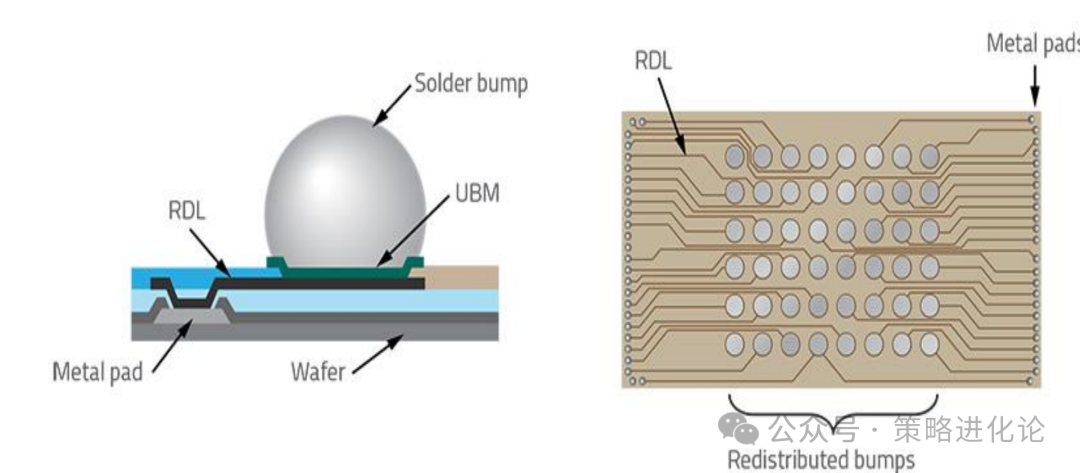

对比传统封装技术,先进封装 I/O 数量多、体积小且高度集成化。在传统的封装技术中,晶圆被切割后通过引线键合的方式实现互联,起到保护芯片的作用。而外部封装则是通过导线架或导线载板与 PCB 基板进行连接,这种封装形式结构简单、成本低廉。但随着集成电路产业的高速发展,市场对于电子设备的小型化、系统化和信息传递速度等的要求不断提高,先进封装逐渐成为行业主流技术。先进封装运用凸块等工艺,采用倒装等键合方式替代传统的引线键合,在缩短互联距离的同时提高 I/O 密度,具有更高的存储带宽和更好的散热效率。同时封装对象由单裸片发展为多裸片,芯片组合由单类型、平面排布向多功能、立体堆叠演变,显著提高了封装空间利用率和芯片系统性能。

二、2.5D/3D封装简介

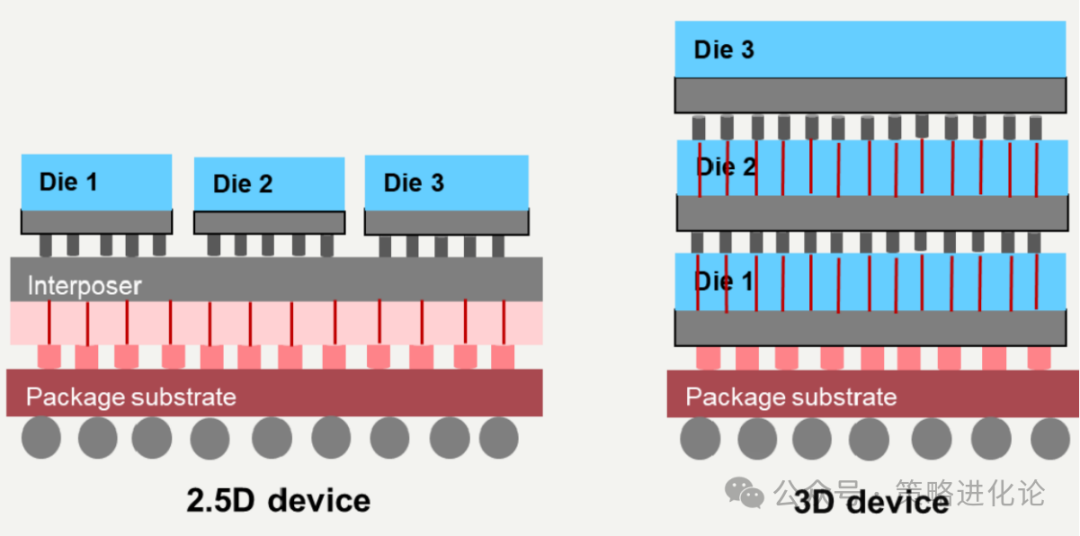

1、2.5D封装可以实现多个芯片的高密度线路连接,集成为一个封装。

在2.5D封装中,裸片堆叠或并排放置在具有硅通孔(TSV)的中介层顶部。硅中介层(Silicon Interposer),可提供芯片之间的互联,在基底和Die之间,起到承上启下的作用。中介层是一种由硅和有机材料制成的硅基板,是先进封装中多芯片模块传递电信号的管道。借助硅中介四通八达的通道,多个Die可以自由的组合在一起,就像一个巨型的地下交通枢纽。相比于直接在基板上进行互连,硅中间层上的连接更短,从而减少了信号传输的延迟和功耗。

另一种是通过“桥”在相邻芯片之间建立连接,首先用具有高 I/O 密度的硅块作为“桥梁”,其次将“桥”嵌入封装基板的空腔内,典型代表是英特尔的EMIB封装。

2、3D封装

相较于2.5D 封装,3D 封装的原理是在芯片制作电晶体(CMOS)结构,并且直接使用硅穿孔来连结上下不同芯片的电子讯号,不需要中介层,直接把每块芯片堆叠到一起,即将存储器或其他芯片垂直堆叠在上面。

3、关键工艺——TSV

要做到2.5D和3D封装,最关键的就是硅通孔技术,简称TSV(Through Silicon Via) TSV作为一种全新的方法,通过数百个孔使上下芯片与印刷电路板相连,是实现三维立体堆叠和系统集成的基础。它是通过在芯片与芯片之间、晶圆和晶圆之间制作垂直通孔,再通过铜、钨、多晶硅等导电物质的填充,实现硅通孔的垂直电气互联,这项技术是目前唯一的垂直电互联技术,是实现3D先进封装的关键技术之一。

由于TSV的诞生,半导体裸片和晶圆可以实现以较高的密度互连堆叠在一起,这也成为了先进封装技术的标志之一。TSV 技术能够使芯片在 3D 堆叠的密度最大,外形尺寸最小,并且大幅改善芯片运行速度,降低功耗。

三、Cowos介绍

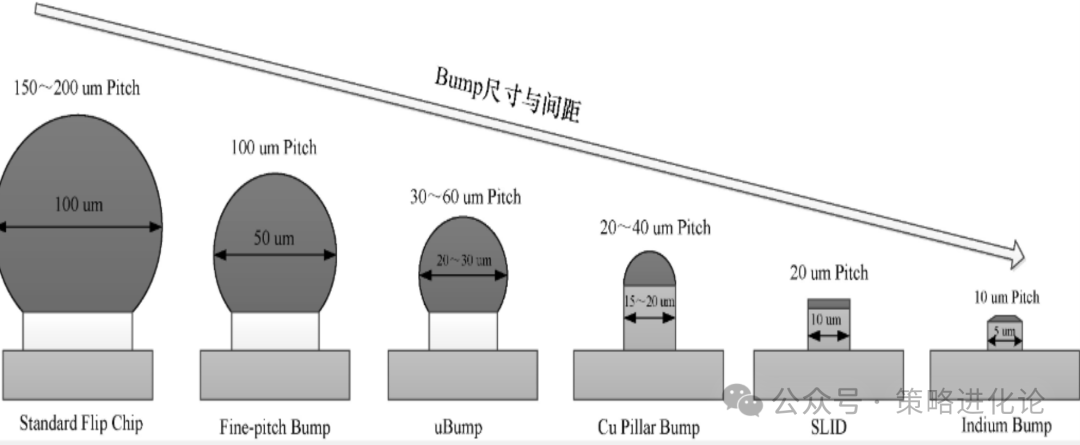

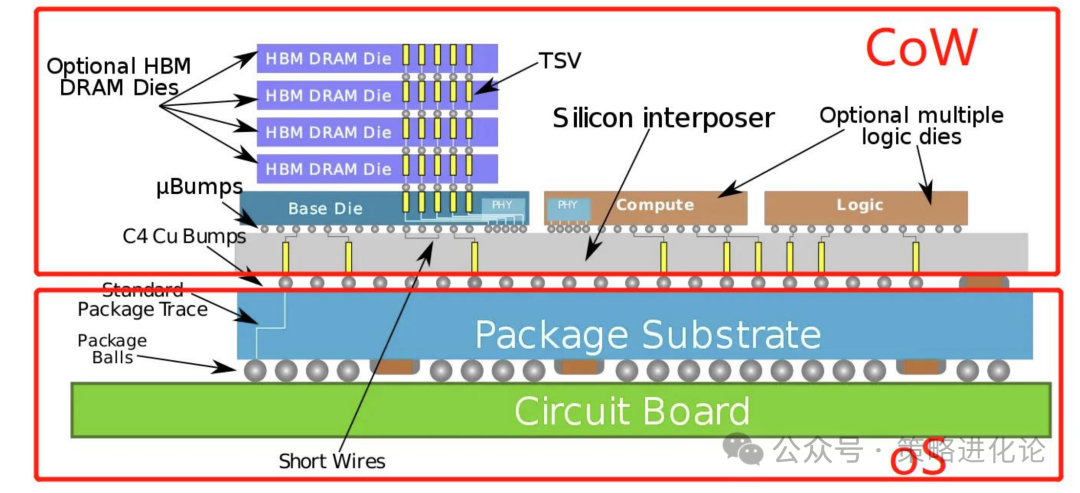

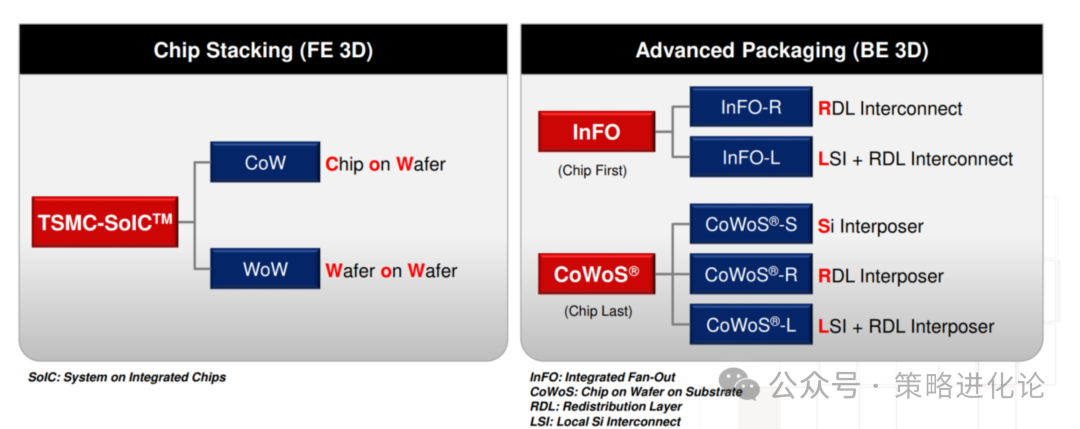

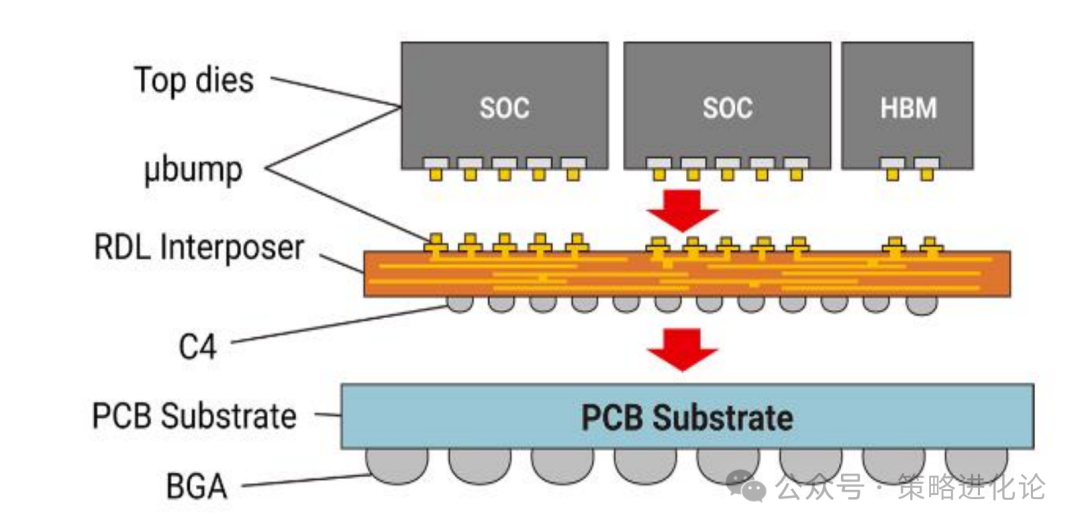

CoWoS(Chip On Wafer On Substrate)是台积电的一种 2.5D 先进封装技术,由 CoW 和 oS 组合而来:先将芯片通过 Chip on Wafer(CoW)的封装制程连接至硅晶圆,再把 CoW 芯片与基板(Substrate)连接,整合成 CoWoS。核心是将不同的芯片堆叠在同一片硅中介层实现多颗芯片互联。在硅中介层中,台积电使用微凸块(μBmps)、硅通孔(TSV)等技术,代替了传统引线键合用于裸片间连接,大大提高了互联密度以及数据传输带宽。

根据不同中介层(interposer)分为 CoWoS-S/R/L 三种类型。

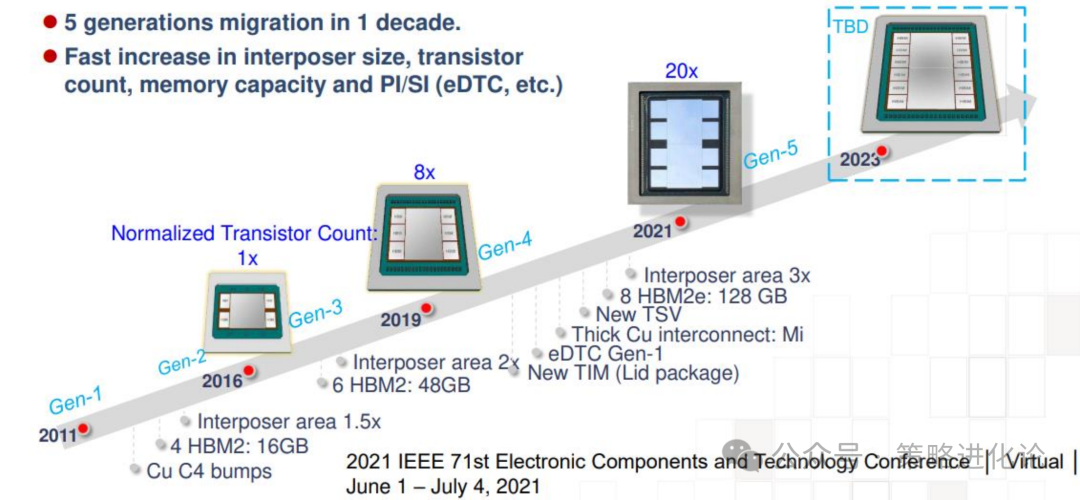

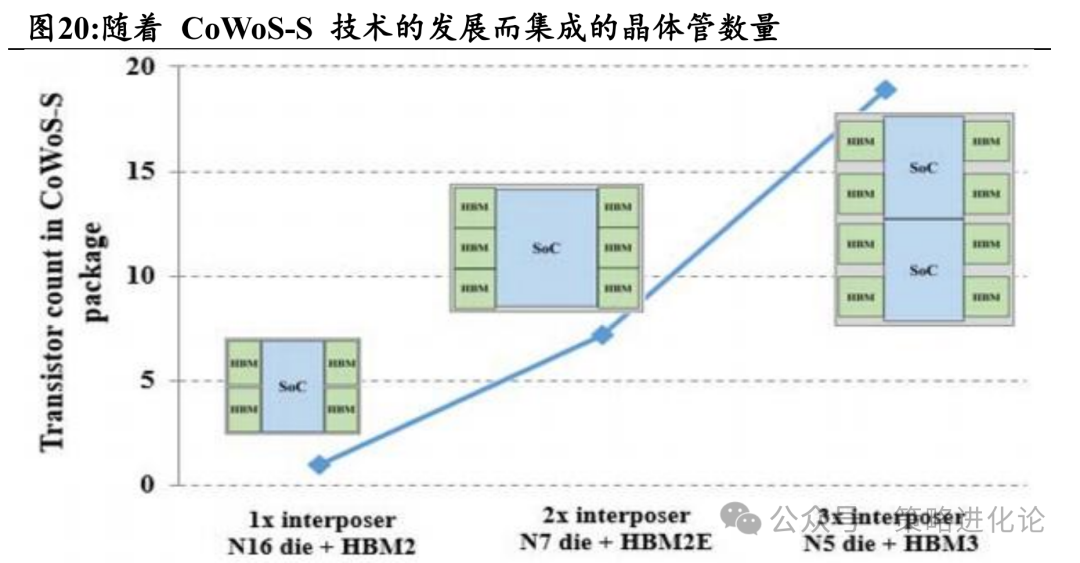

1、CoWoS-S 包括 CoW 和 oS 两部分,芯片间通过 CoW 工艺与硅晶圆相连,再通过凸块将CoW 芯片与基板相连。该技术用微凸块和硅穿孔工艺代替传统引线键合,将不同功能的芯片堆叠在同一个硅中介层上实现互联,具有缩小封装尺寸、降低功耗、提升系统性能的优点。

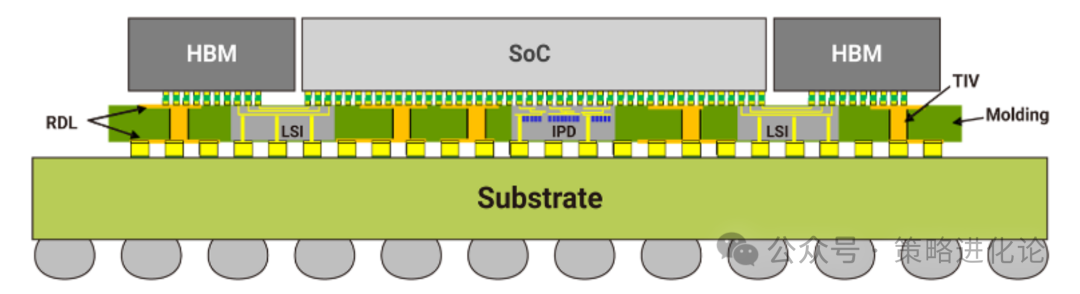

2、CoWoS-R(RDL Interposer)是使用有机基板/重新布线层(RDL)替代了硅(Si)作为中介层的先进封装技术。CoWoS-R 采用 InFO 技术使用 RDL 作为中介层并为 chiplets 之间的互连提供服务,特别是在 HBM(高带宽存储器)和 SoC 异构集成中。RDL 中介层由聚合物和铜走线组成,机械灵活性相对较高,这种灵活性增强了 C4 接头的完整性,并允许新装可以扩大其尺寸以满足更复杂的功能需求

RDL 互连提供良好的信号和电源完整性性能,路由线路的 RC 值较低,可 实现高传输数据速率。共面 GSGSG 和具有六个 RDL 互连的层间接地屏蔽可提供卓 越的电气性能。

3、CoWoS-L(Local Silicon Interconnect and RDL Interposer)是使用小芯片(chiplet)和 RDL 作为中介层(硅桥)的先进封装技术,结合了 CoWoS-S 和InFO 技术的优点,具有灵活的集成性。CoWoS-L 使用内插器与 LSI(本地硅互连)芯片进行芯片间互连,以及用于电源和信号传输的 RDL 层,从 1.5 倍 reticle interposer 尺寸和 1 倍 SoC+4 倍 HBM 立方体开始,并将向前扩展,将包络扩大更大的尺寸,以集成更多芯片

四、在AI芯片上的应用

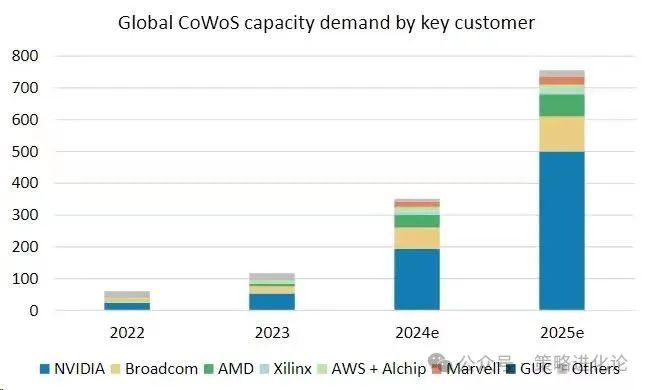

CoWoS的绝大多数需求来自AI

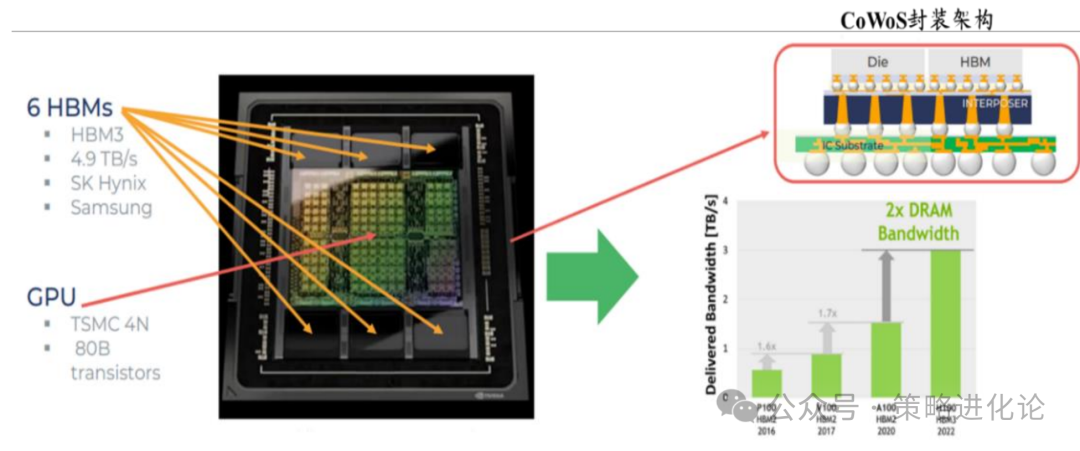

英伟达于 2022 年发布了Hopper Tensor Core GPU,据 Yole 表示,它采用台积电的 CoWos-S 为代表的 Sillicon。Interposer(硅中介层)连接方案将 GPU(台积电 4nm 工艺)与 6 个 HBM 互连。该 产品是市场上第一个使用 HBM3 的产品,提供比英伟达上一代产品 A100 多两倍的 DRAM 带宽。Hopper GPU 与 Grace CPU 配合使用 NVIDIA 的超高速芯片对芯片互连,提供 900GB/s 的带宽,比 PCIe Gen5 快7倍。

除了英伟达,AMD的最新AI GPU产品MI300也导入台积电的CoWoS(2.5D)和SoIC(3D)的技术。此外,还有一系列ASIC芯片,如英特尔的Habana Gaudi、谷歌的TPU(Inferentia和Trainium芯片等。

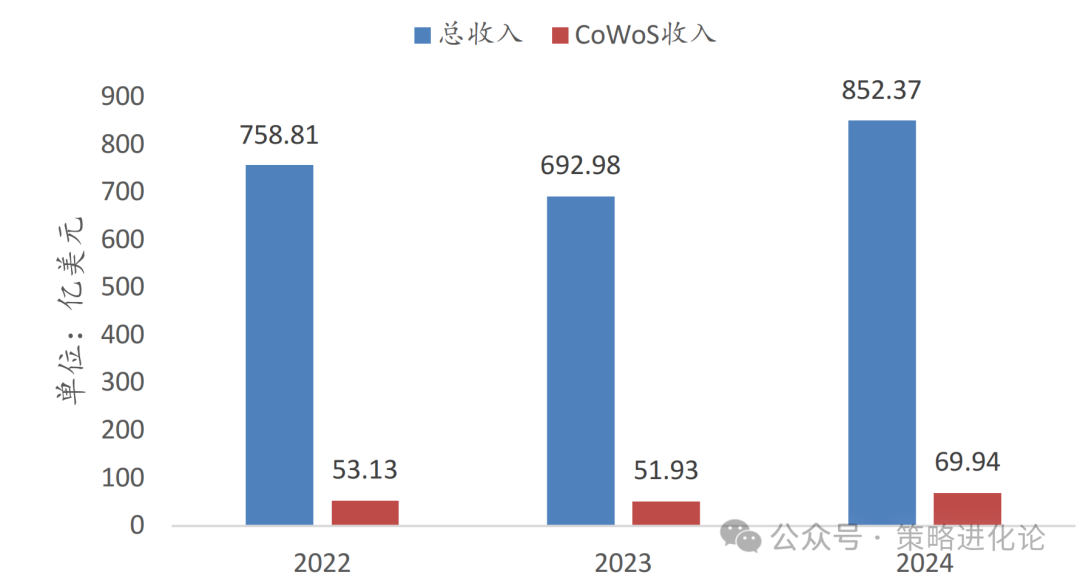

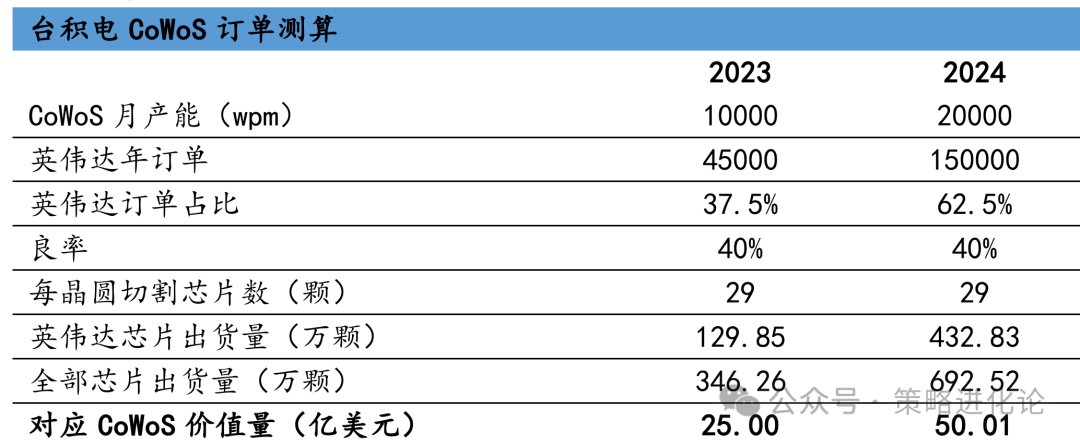

2024年,CoWoS预计为台积电带来70亿美元营收。AI需求驱动下,CoWoS在台积电营收的比重逐渐上升。根据Information Network估计,2022/2023/2024年CoWoS收入占台积电营收的比例将分别达到7.00%/7.49%/8.21%。以台积电2024年全年营收指引852.37亿美元估算,AI将带来约69.94亿美元的CoWoS营收,较2023年同比增长34.69%。

本文转载自:公众号策略进化论

转载内容仅代表作者观点

不代表上海隐冠半导体立场